Los EPYC Rome tendrán un importante rediseño

La incursión de AMD en el mercado de los servidores esta siendo notable, mas aun teniendo en cuenta que esto era un coto privado para Intel hasta antes de ayer, al parecer sus procesadores EPYC basados en Zen están teniendo muy buena acogida en el mercado profesional.

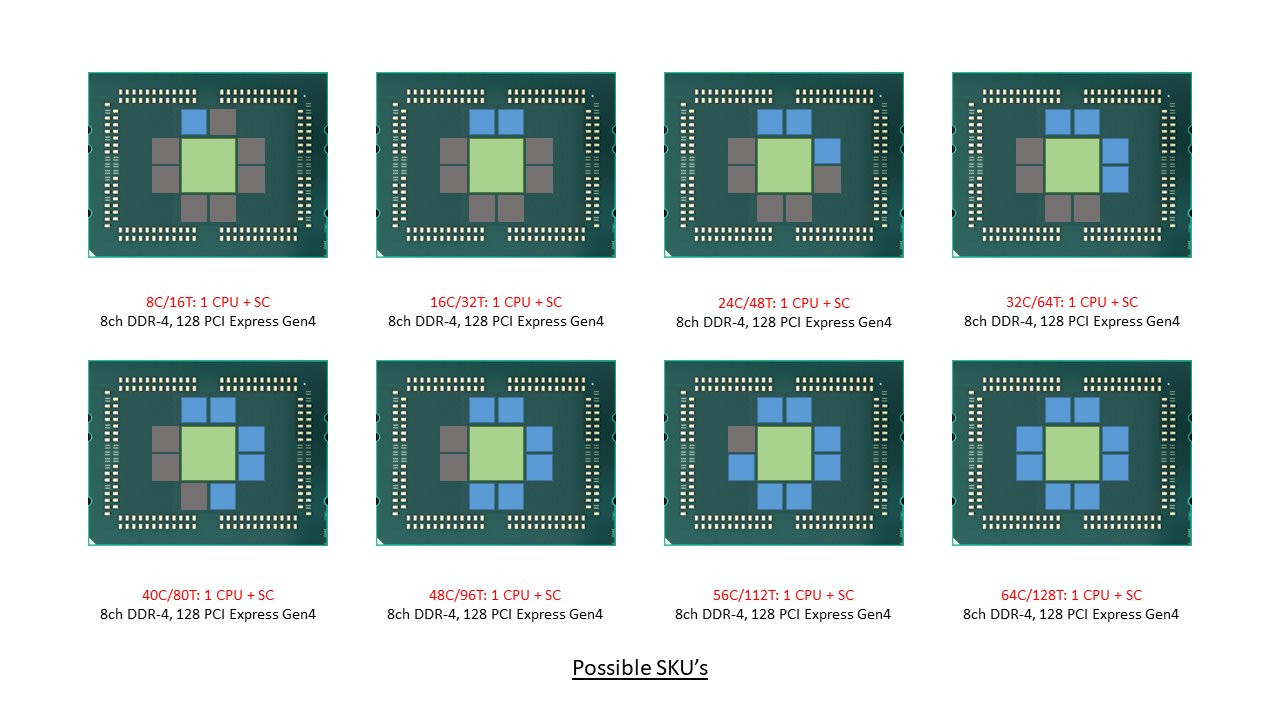

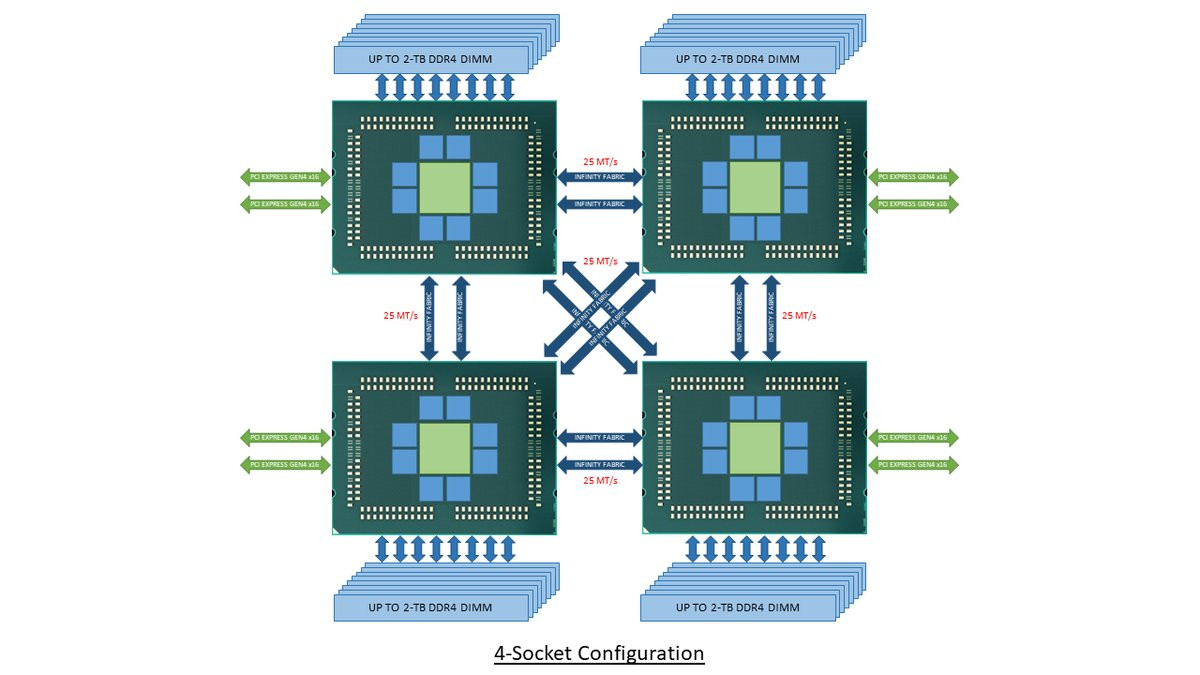

Ahora los nuevos EPYC harán uso de hasta 8 matrices Zeppelin de 8 núcleos cada uno llegando hasta nada menos que los 64 núcleos 128 hilos nada menos. Pero esta nueva generación de EPYC encierra muchos y profundos cambios en la arquitectura, estos cambios buscarían minimizar las latencias que se generan en el interior de estos procesadores, cada vez que los datos deben de saltar entre los CCX, es algo particularmente importante cuando hablamos de procesadores con 64 núcleos.

Uno de los problemas que tiene la arquitectura Zen, en cuanto a su rendimiento, estriba en las elevadas latencias que se producen en ella cuando los datos tienen que saltar entre CCX para seguir su procesado normal. Sin embargo, tal y como está diseñada desde un principio, este tipo de saltos de información, y sus latencias asociadas, era algo que se sabía que iban a suceder.

Para remediar este talón de aquiles de la arquitectura primero que se ha pasado a una integración de 7nm de TSMC que permitirá reducir el consumo y aumentar el número de núcleos así como las frecuencias manteniendo temperaturas, pero lo más importante de los nuevos EPYC Rome será que cada matriz Zeppelin dispondrá ahora de su propio northbridge integrado e independiente que controlará el acceso a memoria, así como a los canales PCI-Express 3.0.

Este nuevo enfoque permite resolver uno de los cuellos de botella que presentaba la arquitectura Zen y que por tanto padecen toda la familia desde los Ryzen, pasando por Threadripper hasta los EPYC, si bien en la gama profesional este problema era mucho mas importante debido a la gran cantidad de memoria que tienen estos sistemas provoca que las latencias de acceso a memoria se acumulen más rápidamente impactando directamente en el rendimiento en operaciones intensivas.

La solución de AMD a este problema es diseñar matrices de CPU con un Northbridge desactivado (la parte del troquel con controladores de memoria y complejo raíz PCIe). Esta solución podría implementarse en sus próximos procesadores EPYC de segunda generación, denominados "Rome", en esta revisión existirá un controlador de sistema centralizado que está rodeado de matrices de CPU.

A diferencia de los procesadores EPYC de la generación actual, esta interfaz de memoria es verdaderamente monolítica, muy similar a la implementación de Intel. El controlador también incluye un complejo raíz PCI-Express gen 4.0 x96, que puede controlar hasta 6 tarjetas gráficas con un ancho de banda de x16, o hasta doce con un ancho de banda de x8.